# EXPERIMENT 1 RC COUPLED CE AMPLIFIER

## I. OBJECTIVES

- To provide the student with all aspects of the frequency response of capacitor-coupled BJT amplifiers.

-To explore the effect of the coupling and bypass capacitors in low frequency.

-To explore the effect of the junction capacitance at higher frequencies.

# **II. INTRODUCTION AND THEORY**

The design procedure of any discrete amplifier can be summarized in the following steps:

- Choose the circuit's configuration that suits the application

- DC design: this part is necessary to define the biasing and the stability of the chosen circuit configuration.

- AC design: to determine the necessary parameters those are needed for the application such as amplifier gain and bandwidth.

In this experiment we will concentrate on the AC design and briefly cover the aspect of the DC design.

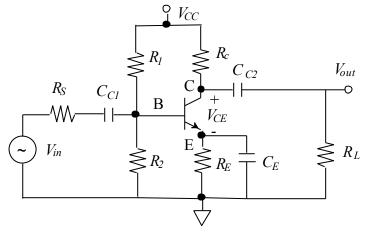

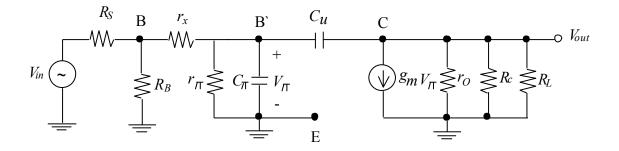

#### Figure 1

A single stage common –emitter amplifier is shown in Figure 1. The biasing circuit consists of two resistors R1 and R2. It is called self-biasing technique that allows us to use a single power supply. The resistance  $R_E$  is necessary to improve the stability of the amplifier, but on the other hand it reduces the gain. Therefore, a capacitor is connected across  $R_E$  to preserve the DC characteristics of the amplifier while eliminating the negative effect of the  $R_E$  on the gain in AC operation. This capacitor is called bypass capacitor  $C_E$ . Other capacitors  $C_{C1}$  and  $C_{C2}$  are used to block the DC current from going in and out of the amplifier stage. This is necessary to maintain

the quiescent point of the amplifier stage in the desired location, which is determined by the DC design procedure. These capacitors are called coupling capacitors.

The above-mentioned capacitors are a lumped element that exist and can be seen and touched in the circuit. Other capacitances cannot be seen or touched only their effects can be observed and must be taken into consideration. This type of capacitance is called a junction or an internal capacitance of the BJT. In general, any two pieces of material (usually conductors or semiconductors) pasted together with insulator material in between will have a capacitance which manifests its effect at high frequencies. This capacitance is not a lumped element as mentioned before. The internal or junction capacitances  $C_{cb}$  and  $C_{be}$  limit the high frequency performance of any active device such as BJT, op-amp, microprocessors, and etc. The high frequency limit of the active devices is referred as  $f_T$  in their data sheets, where  $f_T$  is the frequency at which the gain becomes unity.

The values of the coupling and bypass capacitors must be as high as possible to eliminate any performance degradation in low frequencies. They are in the range of 1-100 uF. In the other hand, it is preferred to have a very low value of the internal capacitance. However, no one has control over the values of the junction or internal capacitance of the device. It only depends on the type of the technology used in the fabrication of the device, the type and the dimension of the active device (BJT, CMOS, and etc.), and the impurity of the semiconductor material.

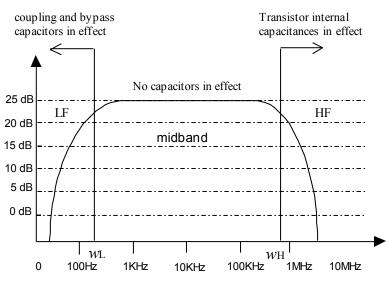

Figure 2 shows the typical frequency response of an amplifier stage. The basic regions of the response are as follows: low frequency region where the equivalent impedance of the coupling capacitors and bypass are not zero, midband region where the coupling and bypass effect has disappeared, and the high frequency region where the effects due to the internal capacitances of the device start to show up. The amplifier transfer function or the overall gain is a frequencies dependent function as given below

$$T.F = \frac{v_{out}}{v_{in}} = A(jw)$$

Figure 2 General frequency response of the amplifier

Note that: the gain of the amplifier falls off at low and high frequencies and is nearly constant at the midband. The general transfer function or the overall gain of the amplifier can be expressed in terms of a frequency dependent functions  $F_L(jw)$  and  $F_H(jw)$ . These two functions are responsible for the fall off of the gain at the low and the high frequency regions. The general form of the amplifier gain is given by

$$\frac{v_{out}}{v_{in}} = A(jw) = A_M F_L(jw) F_H(jw)$$

The bandwidth and the figure of merit of the amplifier are defined as follows The amplifier bandwidth  $BW = w_{1} - w_{2}$  where  $w_{2}$  and  $w_{3}$  are the low and the

The amplifier **bandwidth**,  $BW = w_H - w_L$ , where  $w_L$  and  $w_H$  are the low and the high 3dB points as shown in figure 2.

A figure of merit for the amplifier is its **gain-bandwidth** product,  $GB \equiv A_M(w_H - w_L)$ , where  $A_M$  is the magnitude of the midband gain in volts/volt.

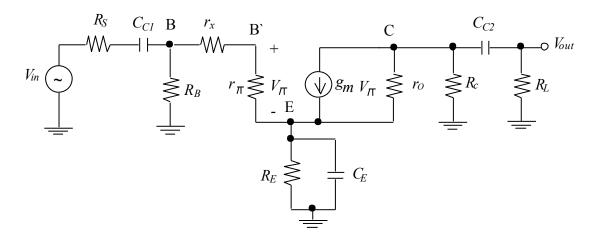

The figures below show equivalent circuit for the amplifier shown in figure 1-a. To determine the upper and lower 3dB points from the equivalent circuit use the superposition theorem to obtain the time constant due to the presence of each capacitance in the circuit. The time constant of the capacitor  $C_i$  is given by

$\tau = C_i R_{io}$

Where  $R_{io}$  is the Thevenin equivalent resistance seen by  $C_i$ .

Figure 3 Equivalent circuit at low frequencies region for the amplifier in Figure 1

Figure 4 Equivalent circuit at high frequencies region for the amplifier in Figure 1

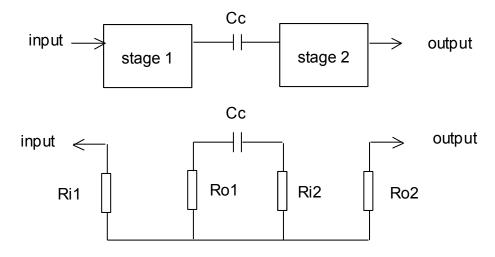

The low frequency analysis of the multistage amplifiers can be simplified by replacing each amplifier stage with the equivalent input and output resistance as shown in Figure 5.

Figure **5** Multistage amplifier

The maximum rating and pin connection for P2N2222A BJT are given below for an example.

Please note that the data sheet of the transistor is in the appendix.

|          |       | Maximum Radings of 12102222A Dipolar fransistor |       |       |  |

|----------|-------|-------------------------------------------------|-------|-------|--|

| $V_{CE}$ | $I_C$ | β                                               | $P_D$ | Freq  |  |

| (V)      | (mA)  | max./typical                                    | (mW)  | (MHz) |  |

| 40       | 800   | 300/100                                         | 500   | 300   |  |

Maximum Ratings of P2N2222A Bipolar Transistor

BJT pinout is given below. Pin 1= Collector, Pin 2=Base, Pin 3= Emitter

## **III. PROCEDURE**

1- Build the circuit shown in Figure 1 using the following components listed in the table below

| R1    | R2   | R <sub>E</sub> | R <sub>C</sub> | R <sub>S</sub> | R <sub>L</sub> | V <sub>CC</sub> | C <sub>C1</sub> | C <sub>C2</sub> | CE    |  |

|-------|------|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-------|--|

| 75K   | 33K  | 4.7K           | 4.7K           | 1K             | 10K            | 15V             | 0.1µF           | 0.1µF           | 0.1µF |  |

| 1 1 . | .1 . | •              | .1 0           | 1              | 1              | •               |                 |                 |       |  |

While assembling the circuit, use the 3-legged transistor mount for the BJT.

- 2- Conduct a DC measurements to determine the location of the operating point and  $\beta$ . In other words you need to measure  $I_C$ ,  $V_{CE}$ , and  $I_B$ .

- 3- Apply a sinusoidal signal to the input and adjust the amplitude so that the output waveform has no distortion (The amplitude adjustment must be done in the midband region). Perhaps amplitude of 25mV (50 mV peak-to-peak) would work. Please note that the amplitude of the input signal will be kept constant during this experiment.

- 4- Sketch the amplitude response as a function of the input signal frequency. (Use a semilog graph paper, the frequencies are located on horizontal axis (log scale) and the amplitude is in dB located on the vertical axis (linear scale) as shown in figure 2. (Take extra points on the curve whenever you encounter a significant change in output while input is kept constant).

- 5- Repeat steps 3 and 4 using  $C_{C1}=C_{C2}=C_E=22\mu F$ .

- 6- Tabulate all the above data.

#### **IV. QUESTIONS**

- 1- What is the maximun allowable ac output swing in step 2?

- 2- Discuss the influence of the bypass, coupling, internal, and stray capacitances on the frequency response.

- 3- What is the purpose of capacitor's  $C_{C1}$  and  $C_{C2}$ ? 4- In Fig.1 (a)  $C_E = 0.1 \ \mu\text{F}$ . This value is changed to 22  $\mu\text{F}$  in step 5. Based on your theoretical knowledge, how do you expect the lower 3 dB to change when C<sub>E</sub> is increased to 22 μF?

5- Does C<sub>E</sub> have any effect on upper 3 dB point? Why?